The Holdt Archives

|

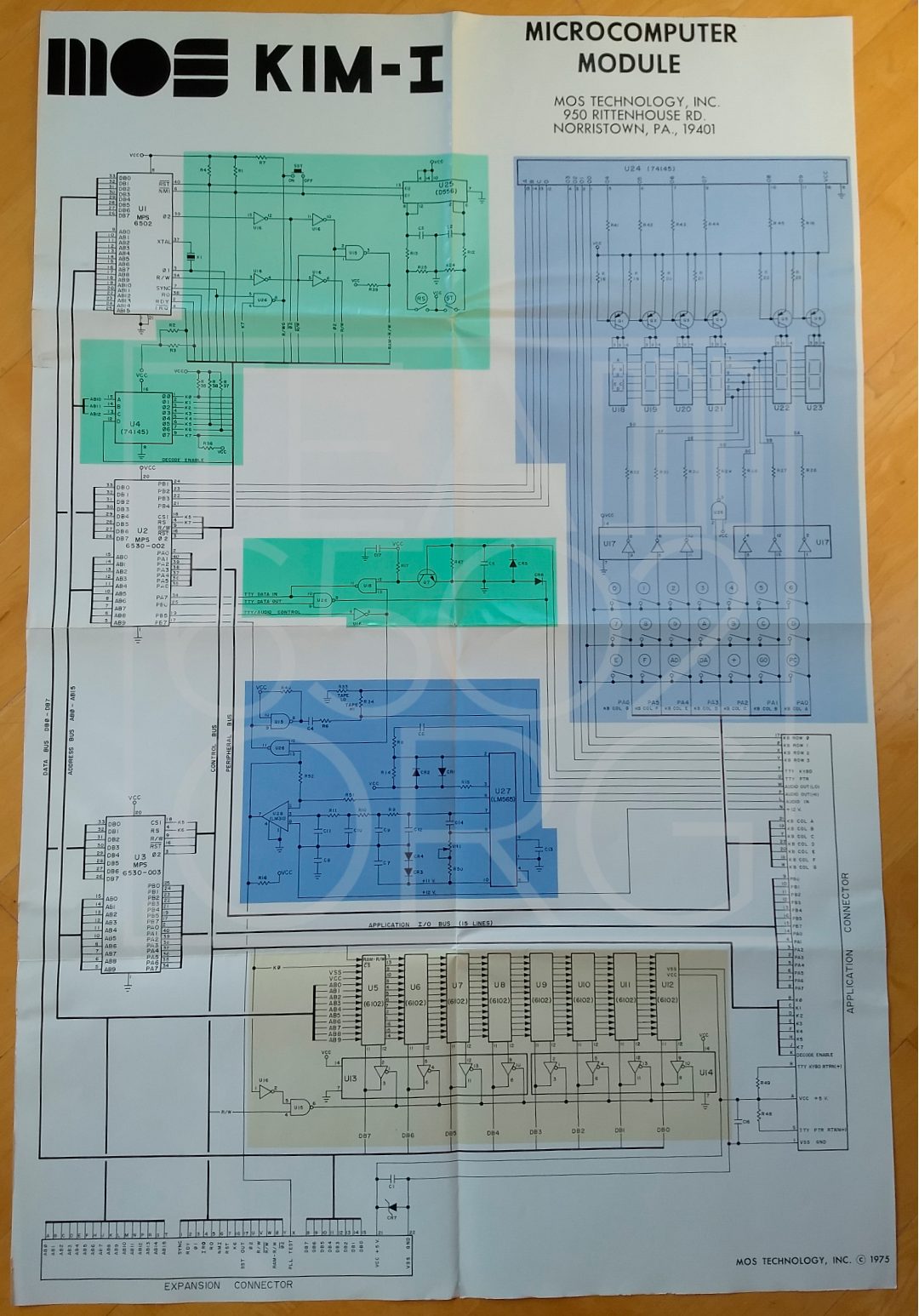

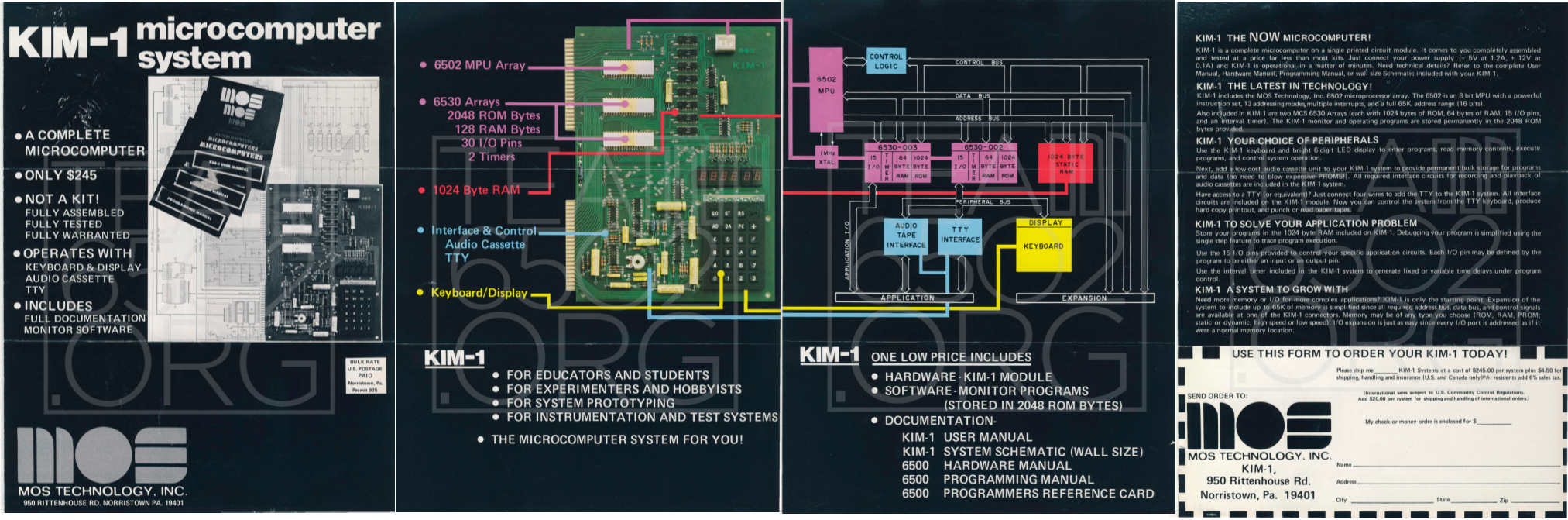

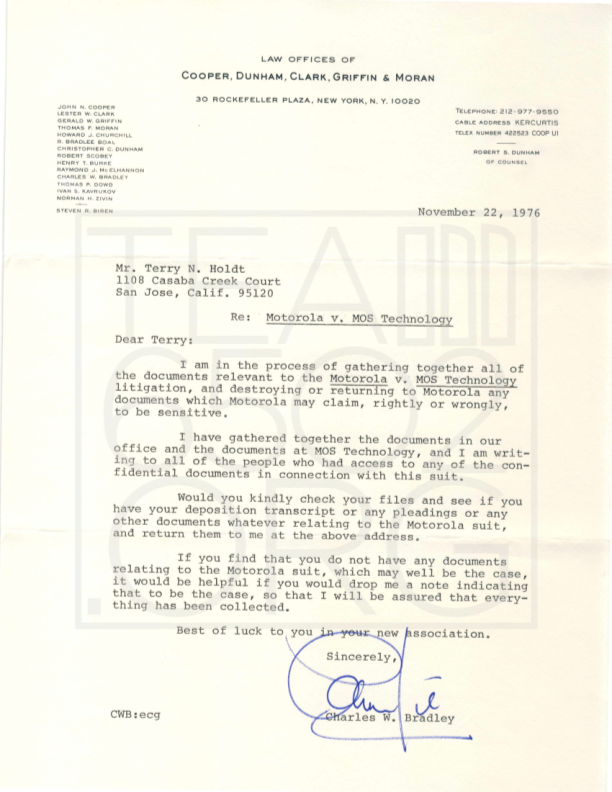

Terry Holdt was the Product/Program Manager of Microcomputers for MOS Technology from 1974-1976. He was part of the original team of eight Motorola employees who left the Semiconductor Products Division of Motorola in 1974 where he was serving as Product Manager for MOS P/N Products, including the Motorola 6800 family of microprocessors, to pursue the goal of creating the world's first affordable microprocessor at MOS Technology. It was Holdt who one Motorola manager appealed to in an effort to prevent a brain drain of talent from the 6800 microprocessor team, showing up at his front door one night to implore him, "Please stay. If you go, everyone will go." Of course, believing in Chuck Peddle's vision regarding the untapped potential of a low-cost microprocessor--the creation of which Motorola declared it was unwilling to pursue--Terry went, and many others in the 6800 team did, too. The rest is history. In a resume dating to 1976, Terry describes the wide variety of his duties at MOS Technology, noting that he reported to the company president, John Paivinen, and had responsibility for "the overall program planning and execution of efforts surrounding the microprocessor system." He describes participating in decisions regarding "the product definition, pricing, support activities (hardware and software), customer interface, advertising, factory planning, allocation of available resources, and process development," qualifying his efforts in "process development" by noting that while it was a task he agreed to perform on an "interim basis" because "management of the process development group was lacking," the supervision of that labor force as well as "a portion of the engineering of the N Channel Silicon Gate Depletion Load 5 Volt Process" evolved into a "nearly full time job." As a result, Terry explains that while his "primary function was to manage the overall microprocessor program," his primary effort was "management and technical assistance in the process development area." This intensive focus on process development is evident in the volume as well as technical and detailed nature of the preserved documents discovered in Terry's home in 2018. Indeed, the documents in the Holdt Archives which relate to process development--primarily three binders labeled N-Channel Physical Considerations, Depletion and Ion, and Int. Doc Wafer Fab 1--tell a detailed and fascinating story about the collaborative effort that resulted in the specific 019-process used to create the 6500 family of microprocessors. This effort included not only MOS Technology engineers, but engineers whose published writings were photocopied, annotated, and distributed to other engineers by Holdt--writings such as Robert Crawford's Mosfet in Circuit Design, an article concerning ion implantation by John R. Edwards and George Marr of Bell Labs, and several chapters from Andy Grove's 1967 book on microprocessor production, Physics and Technology of Semiconductor Devices. In fact, it was the information gathering, sharing, sorting, and testing efforts--so carefully conducted, then preserved, by Holdt--which were to credit for the knowledge and expertise he acquired to draft his report, Some Physical Considerations on the N-Channel Silicon Gate Depletion Load "019" Process. This report synthesized that information for the benefit of both the process and design teams at MOS Technology, influencing not only the transistor layout of the 6502--now hailed as a masterpiece of computer architecture--but the highly technical and intricate 50-step production process (also preserved in the Holdt Archives) used by MOS Technology to produce the world's first affordable microprocessor. Because Holdt's responsibilities at MOS Technology were so varied, the historical documents provide not only a detailed window into the process development, but also a glimpse into the workings of MOS Technology across a wide variety of other fronts as well: including P&L, sales, marketing, and the creation of instructional documents which accompanied MOS Technology products--such as the KIM-1, MOS Technology's single board computer--at point of purchase. Therefore, included in the Holdt Archives are not only internal documents such as notes from brainstorming sessions between MOS Technology engineers, memos relating to various production challenges, and MOS testing procedures and results, but MOS Technology documents that were either released publicly or early versions of such documents noting errata. These include letters to customers, product manuals, MOS brochures, marketing materials, catalogs of MOS products, a poster for the KIM-1 Board, order forms for MOS products, and more. NOTES: - Many of the documents below are partial samples only. There are also additional documents in the archives not featured below. For additional information, contact team6502.org. - Single page documents are featured as images only. Multiple page documents are offered as PDFs. Click on image to open and view PDF. |

Microprocessor Production

Process-Related Documents

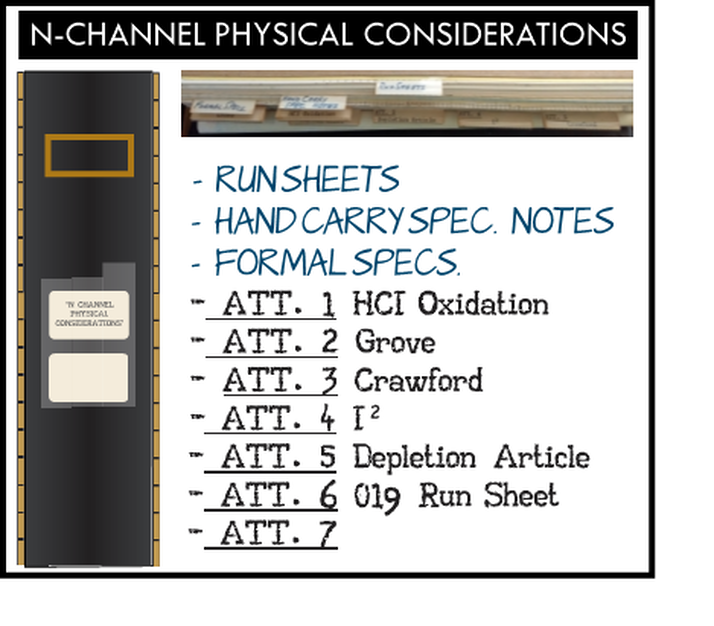

N-Channel Physical Considerations Binder

Terry Holdt's N-Channel Physical Considerations binder contains a variety of documents relating to microprocessor production, including hand written and typewritten specifications detailing a highly precise and intricate 50-step production process, a variety of articles and book chapters that were consulted and annotated to solve various production challenges, as well as a wide array of testing results. There are 10 tab dividers in the binder, labeled as noted in the accompanying, above illustration. All documents are presented in the order in which they appear in the binder.

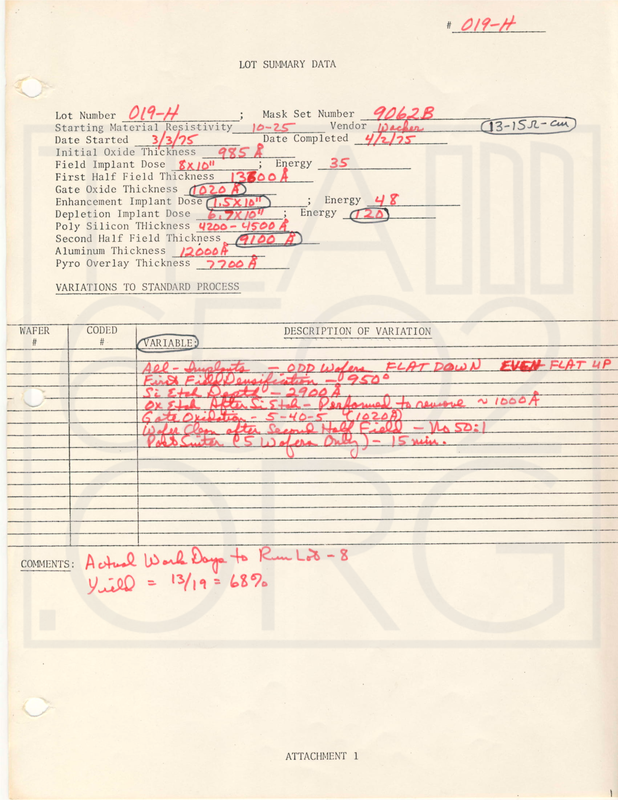

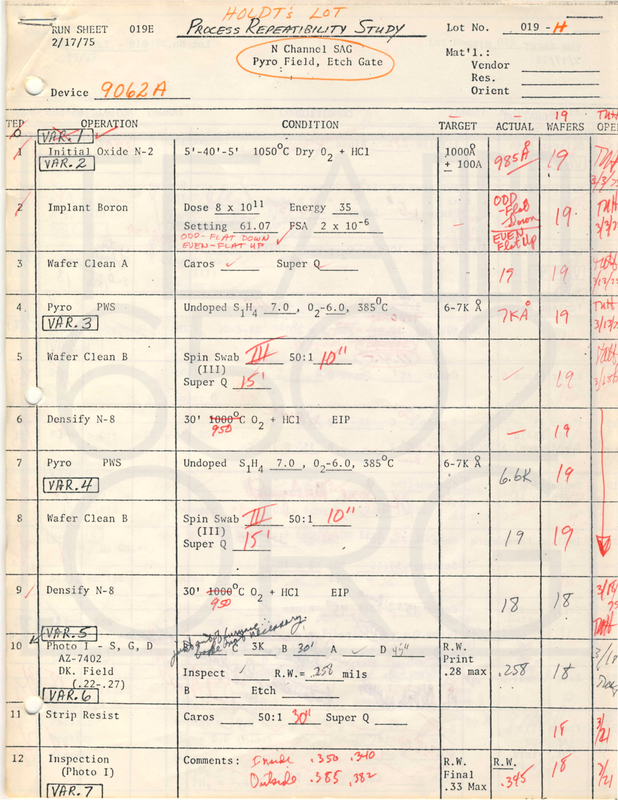

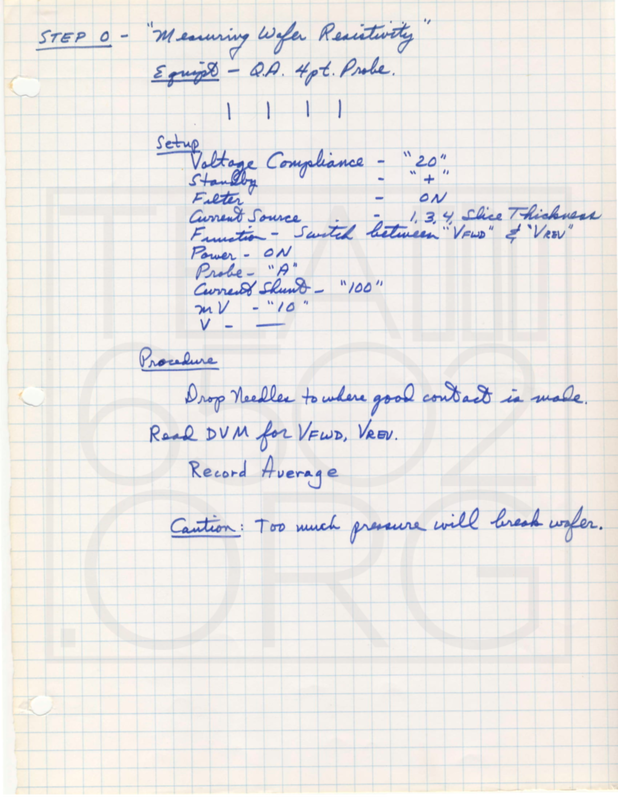

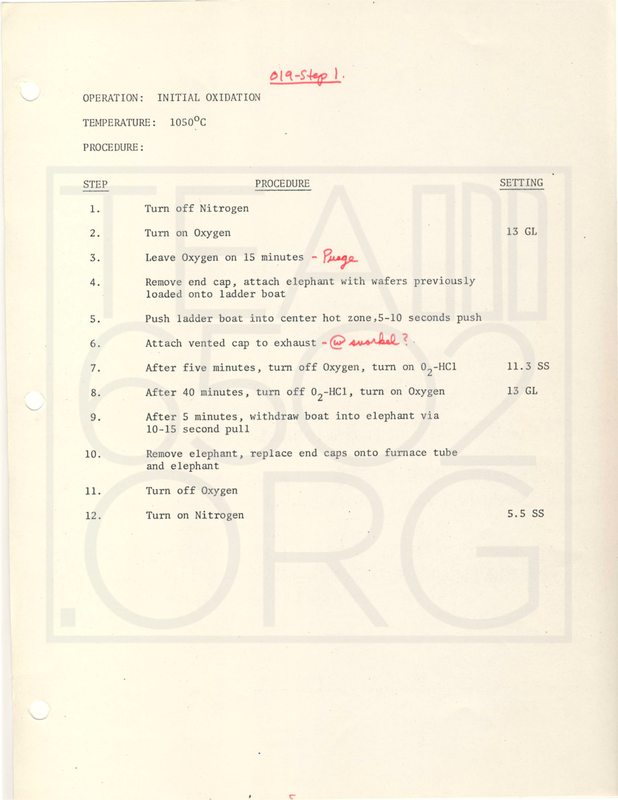

Tab #1: Run Sheets

Tab #2: Hand Carry Spec Notes

Tab #3: Formal Specs

Tab #7: ATT. 4: I22 (ion)

Tab #9: ATT. 6 019 Run Sheet

Tab #10: ATT. 7

No additional title was given to ATT. 7 tab, however, this section consists of Lot 0H-19 test results.

Tabs ATT. 1, ATT. 2, ATT. 3, and ATT. 5

Tabs ATT. 1, ATT. 2, ATT. 3, and ATT. 5 contain highly annotated photocopies of the following articles and chapters from books. Below are their titles.

ATT.1 HC1 Oxidation

ISSCC 75/Wednesday, February 12, 1975/Brandywine Ballroom/3:10-5:45

WMP6.3: High Quality Si02 for Integrated Circuits (handwritten by Holdt after title: "- Hcl")

SESSION VI/INVITED: Frontiers of Technology

Rudolph Kreiger

Bell-Northern Research, Ltd.

Ottawa, Canada

ATT. 2 Grove

Chapters from book Physics and Technology of Semiconductor Devices by Andrew S. Grove, 1967:

- 2 Thermal Oxidation

- 3 Solid State Diffusion

- 4 Elements of Semiconductor Physics

- 6 p-n Junctions

- 9 Theory of Semiconductor Surfaces

- 10 Surface Effects on p-n Junctions

- 11 Surface Field-Effect Transistors

- 12 - Properties of the Silicon-Silicon Dioxide System

ATT. 3 Crawford

Mosfet in Circuit Design by Robert Crawford, June 1967.

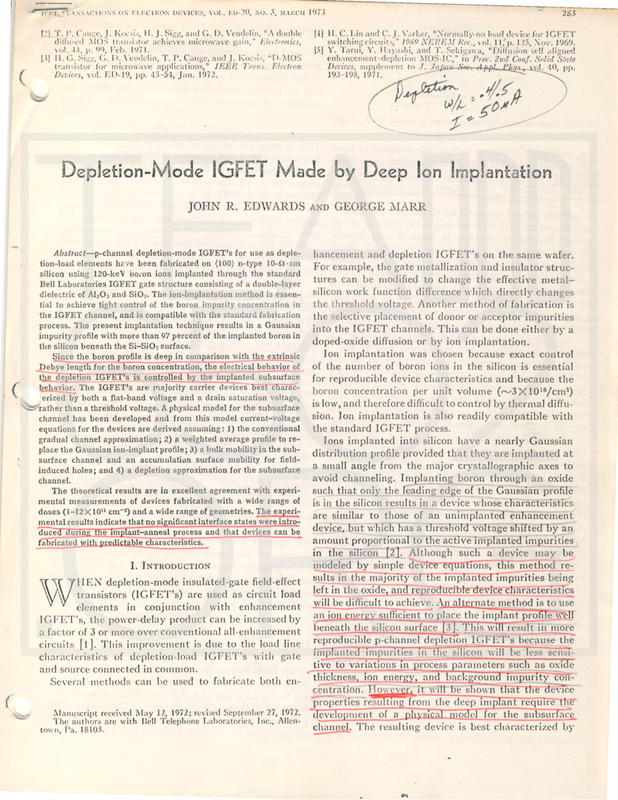

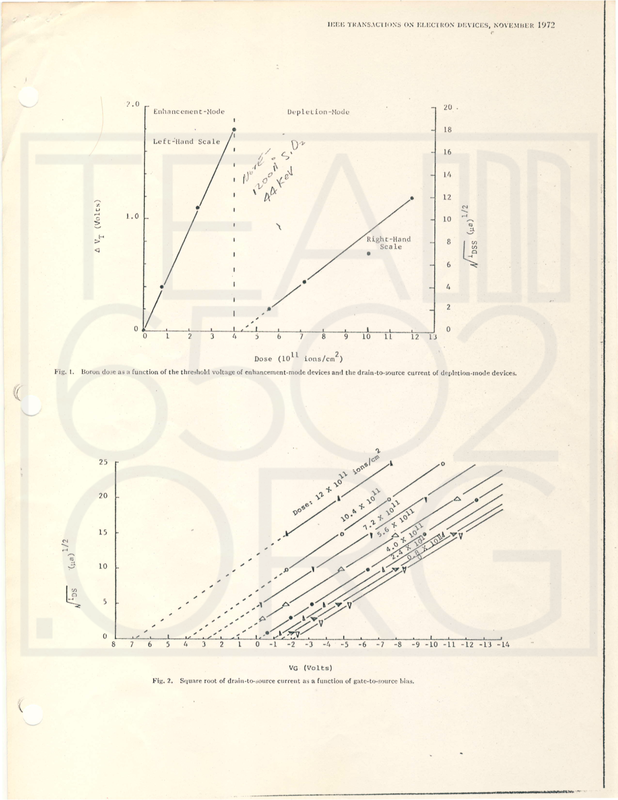

ATT. 5 Depletion Article

"Depletion-Mode IGFET Made by Deep Ion Implantation" by John R. Edwards and George Marr, IEEE Transactions on Electron Devices (Volume: 20 , Issue: 3 , March 1973 )

ATT.1 HC1 Oxidation

ISSCC 75/Wednesday, February 12, 1975/Brandywine Ballroom/3:10-5:45

WMP6.3: High Quality Si02 for Integrated Circuits (handwritten by Holdt after title: "- Hcl")

SESSION VI/INVITED: Frontiers of Technology

Rudolph Kreiger

Bell-Northern Research, Ltd.

Ottawa, Canada

ATT. 2 Grove

Chapters from book Physics and Technology of Semiconductor Devices by Andrew S. Grove, 1967:

- 2 Thermal Oxidation

- 3 Solid State Diffusion

- 4 Elements of Semiconductor Physics

- 6 p-n Junctions

- 9 Theory of Semiconductor Surfaces

- 10 Surface Effects on p-n Junctions

- 11 Surface Field-Effect Transistors

- 12 - Properties of the Silicon-Silicon Dioxide System

ATT. 3 Crawford

Mosfet in Circuit Design by Robert Crawford, June 1967.

ATT. 5 Depletion Article

"Depletion-Mode IGFET Made by Deep Ion Implantation" by John R. Edwards and George Marr, IEEE Transactions on Electron Devices (Volume: 20 , Issue: 3 , March 1973 )

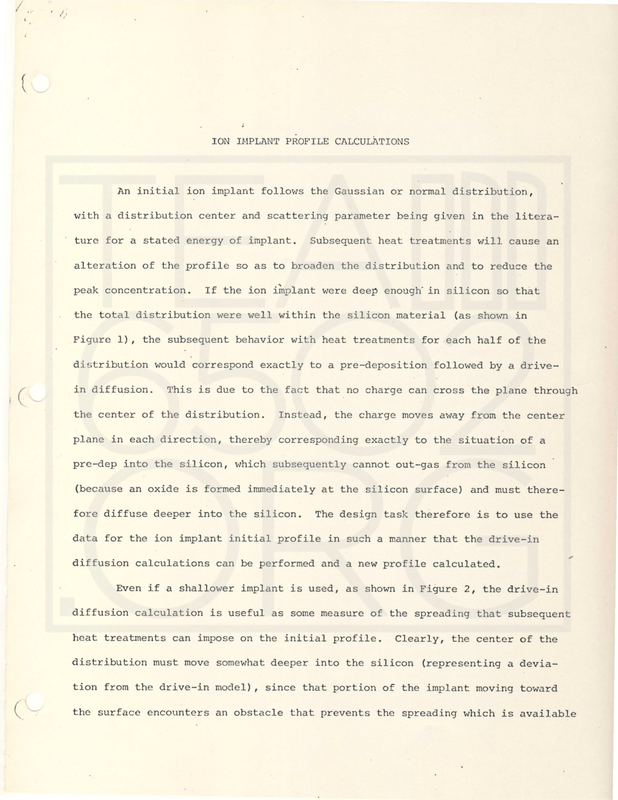

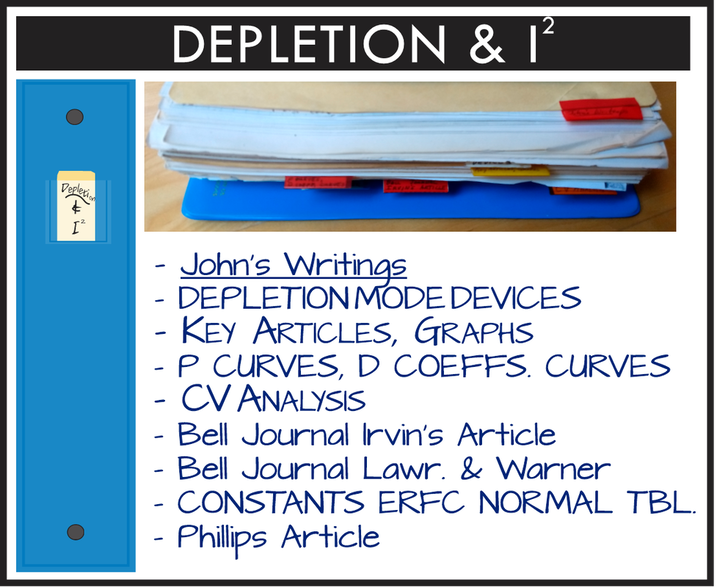

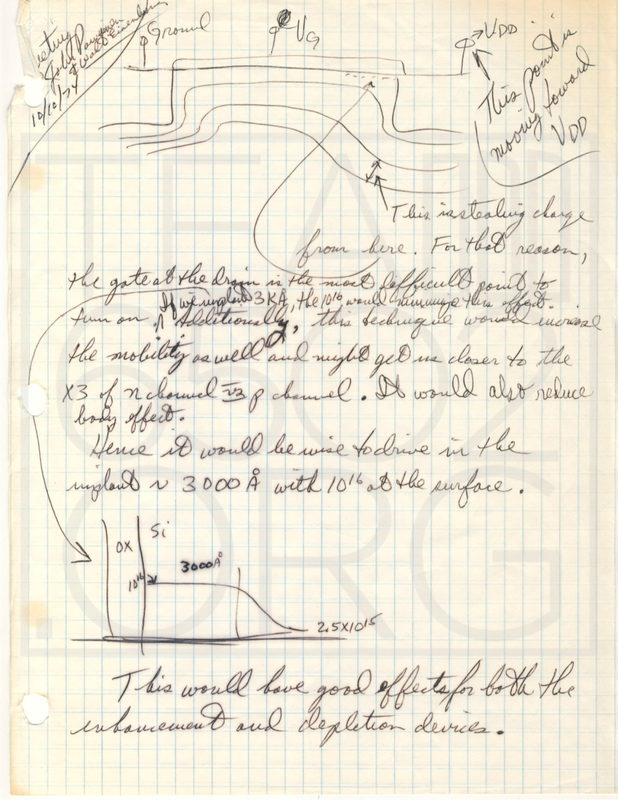

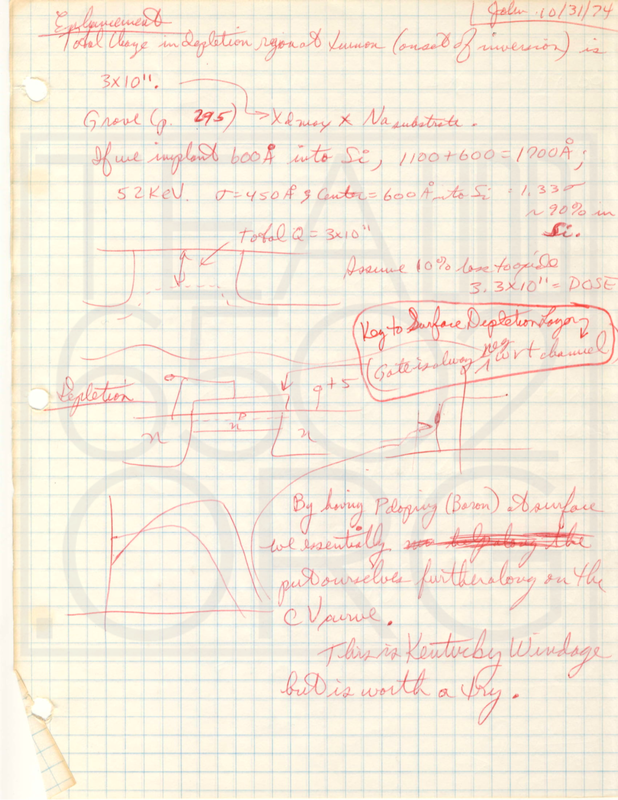

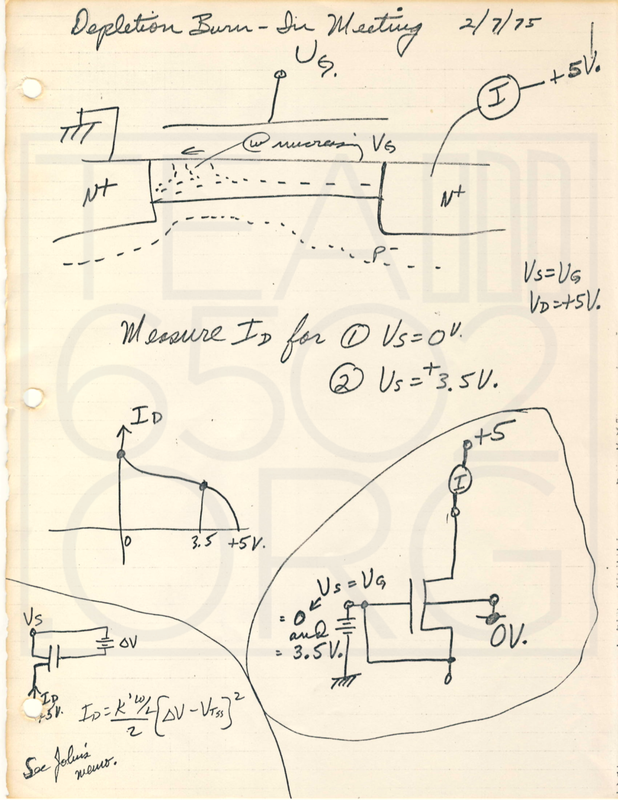

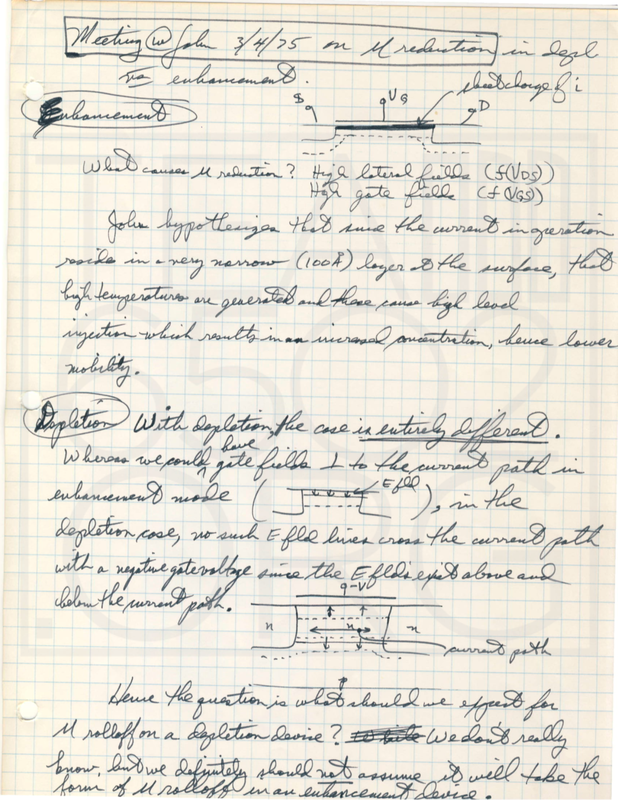

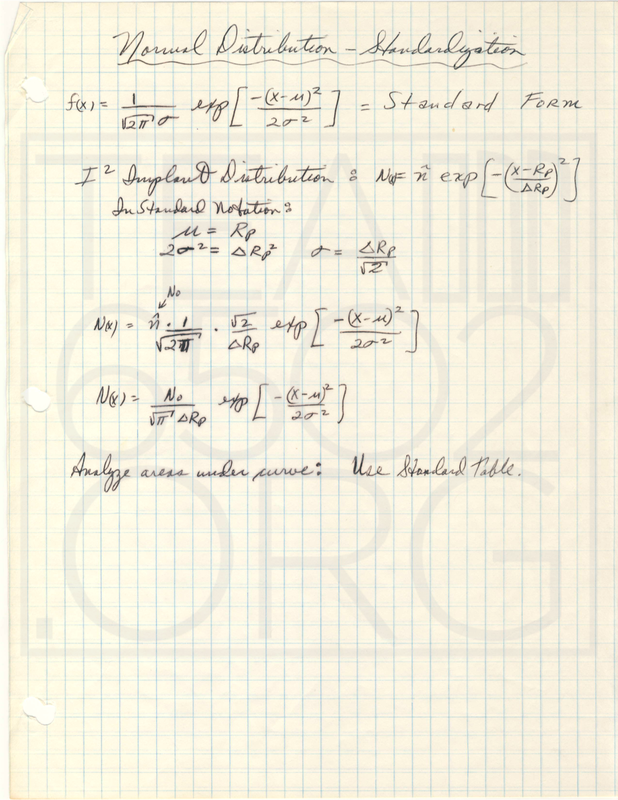

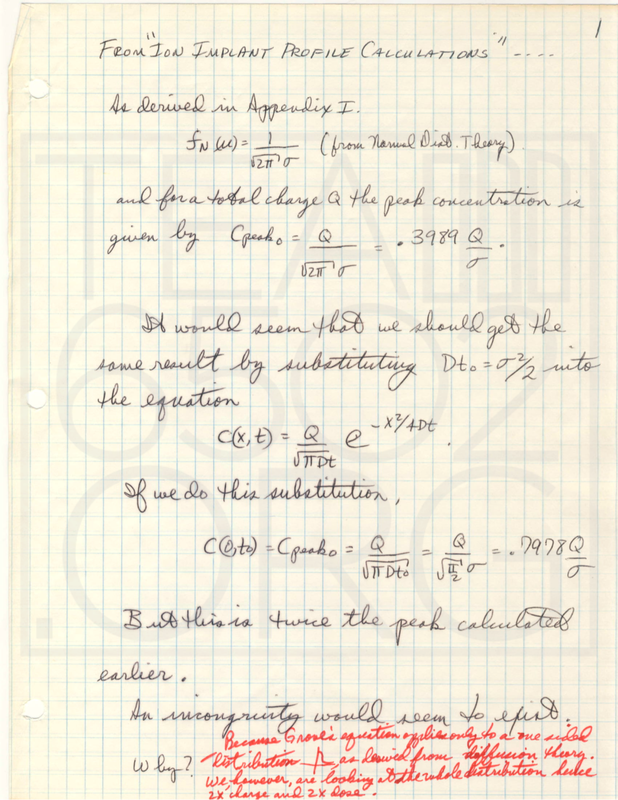

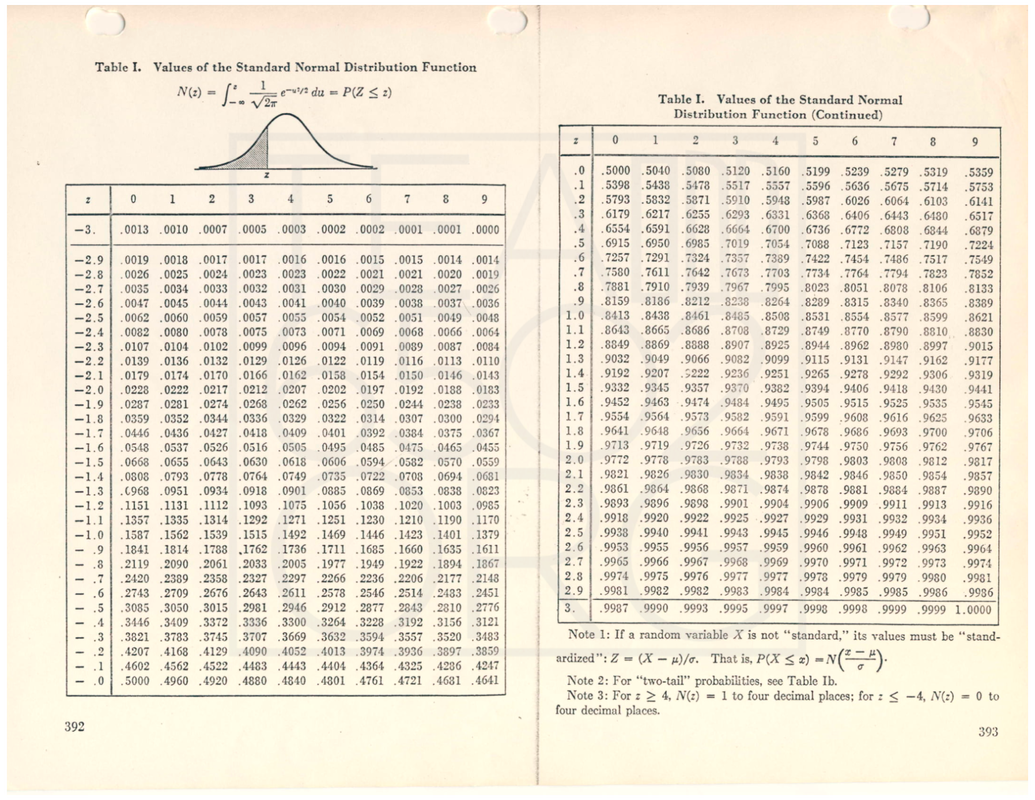

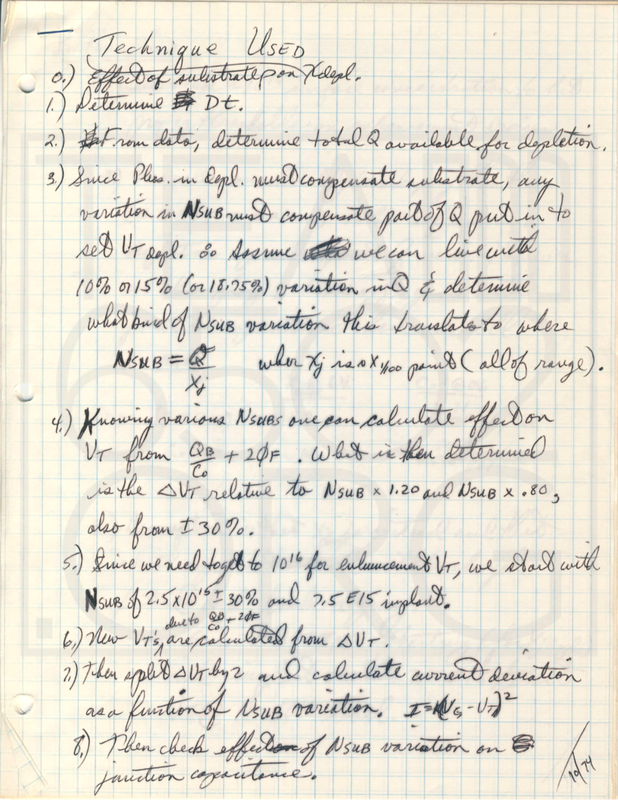

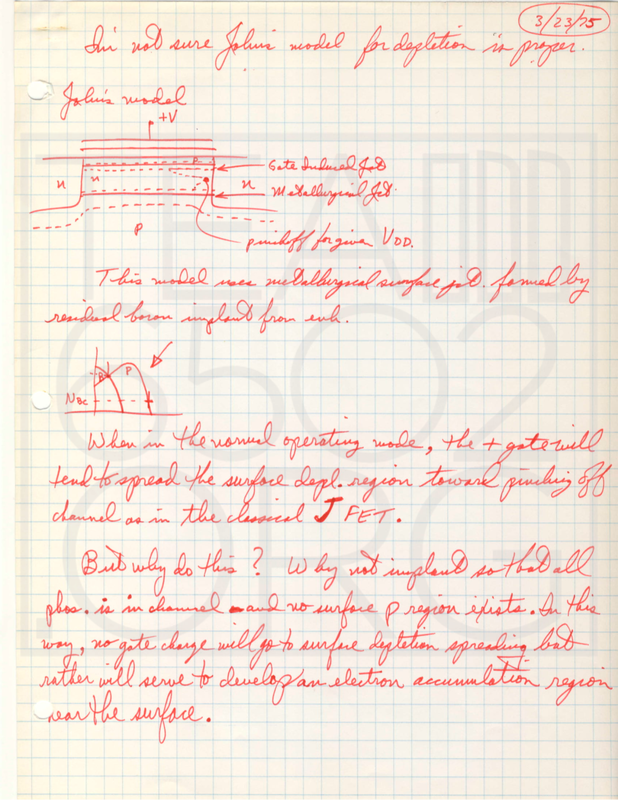

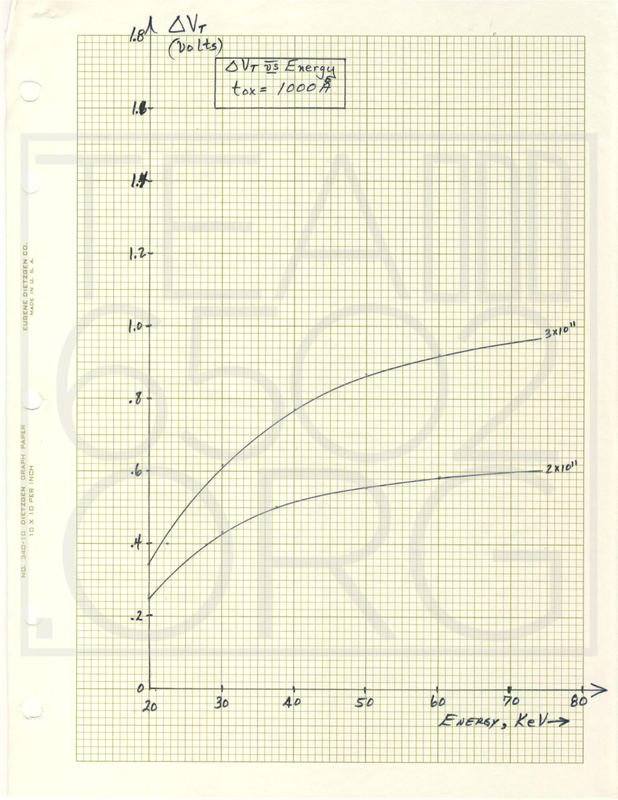

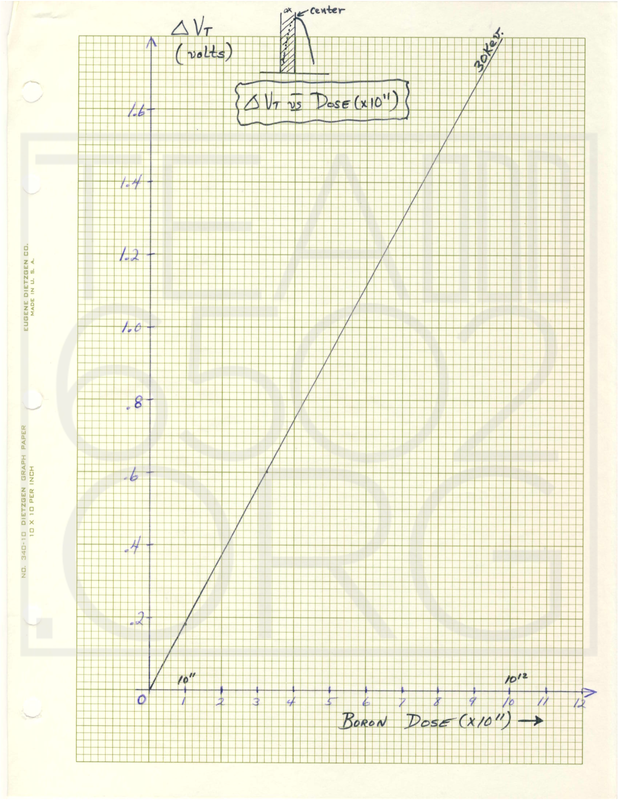

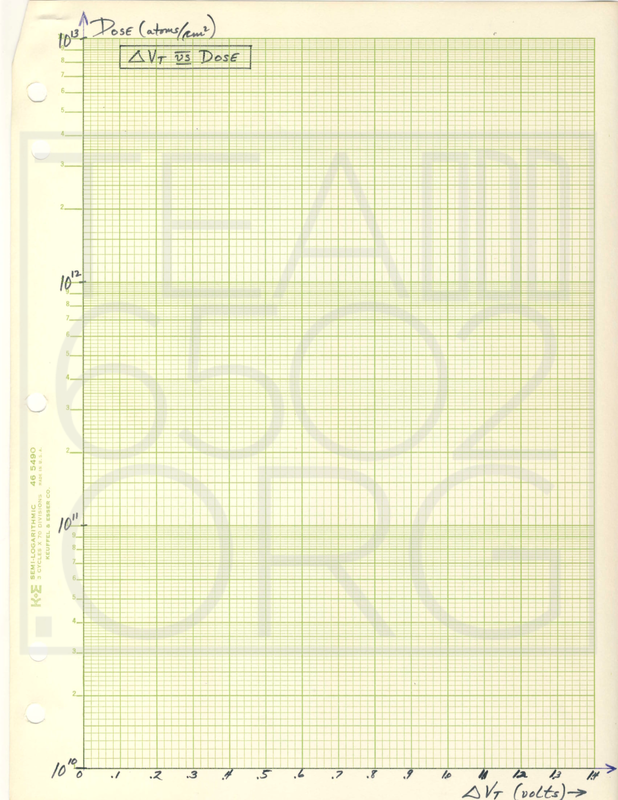

Depletion and I2 (Ion) Binder

Terry Holdt's Depletion and Ion Binder binder contains a variety of documents that show the collaborative effort of the engineers who worked on depletion and enhancement issues surrounding the production of the 6500 family of microprocessors. These documents include various handwritten notes taken by Holdt during meetings with other MOS Technology engineers such as John Paivinen and Walt Eisenhower, various technical reports written by Paivinen, pages of formulas relating to depletion and enhancement, photocopies of published articles annotated by Holdt, information on settings and other issues relating to depletion mode devices, CV Analysis test results, and more. There are 9 tab dividers in the binder, labeled as noted in the accompanying, above illustration. All documents are presented in the order in which they appear in the binder.

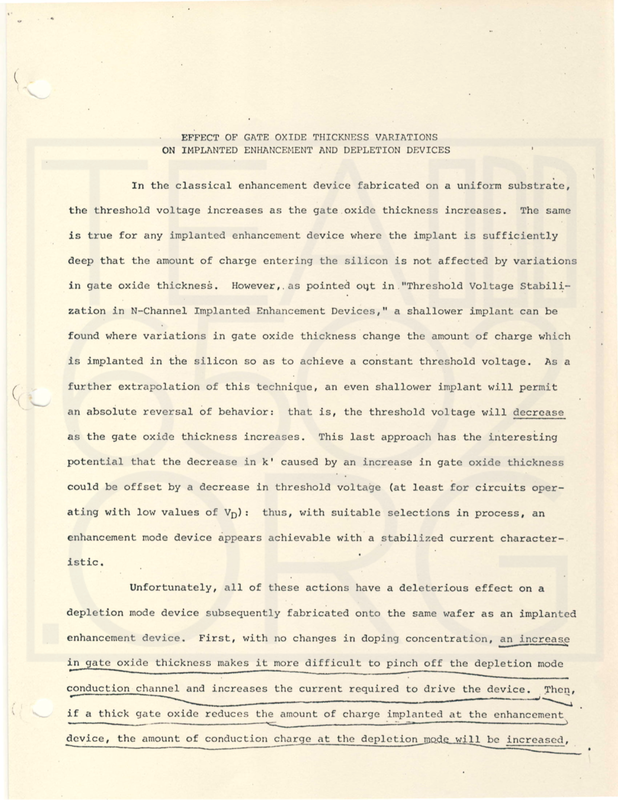

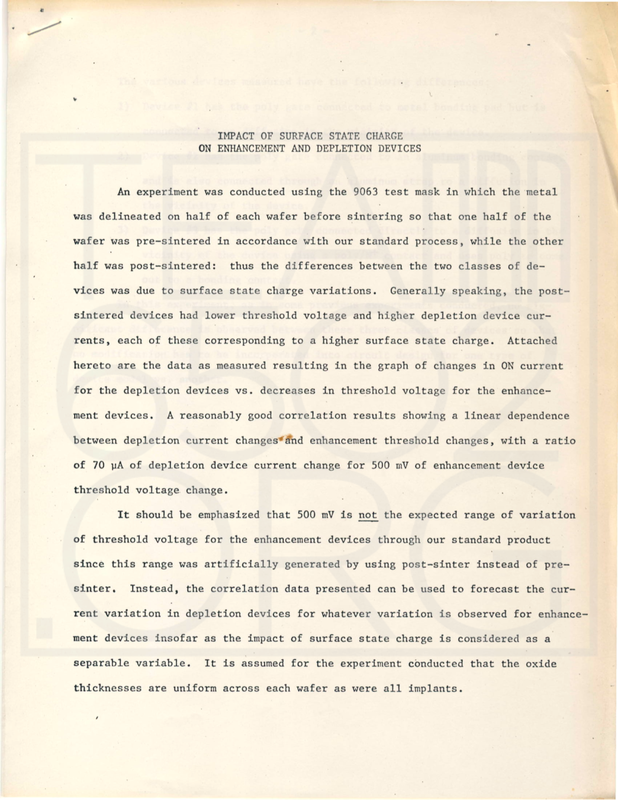

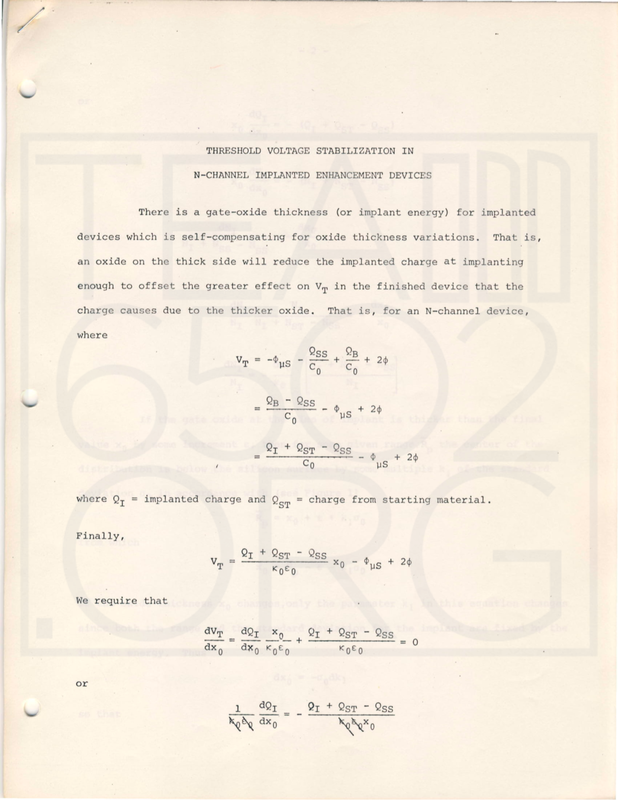

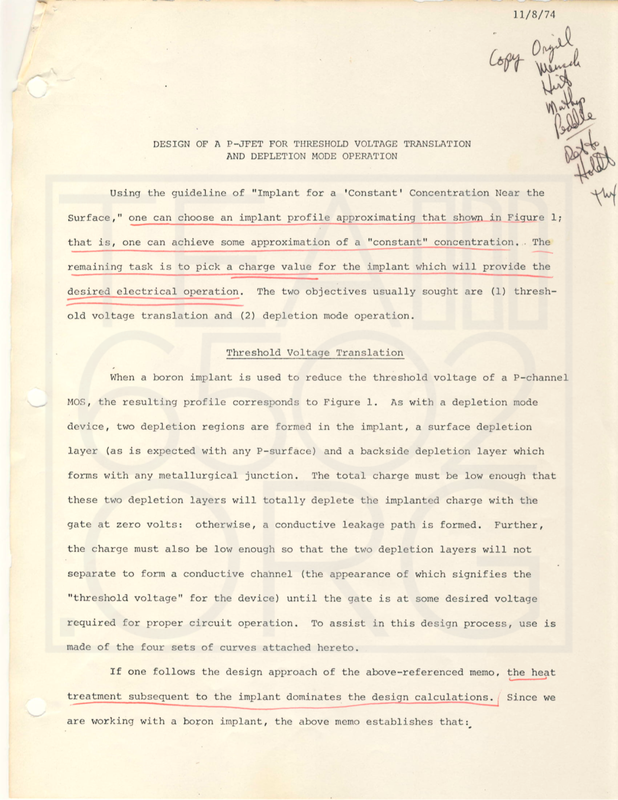

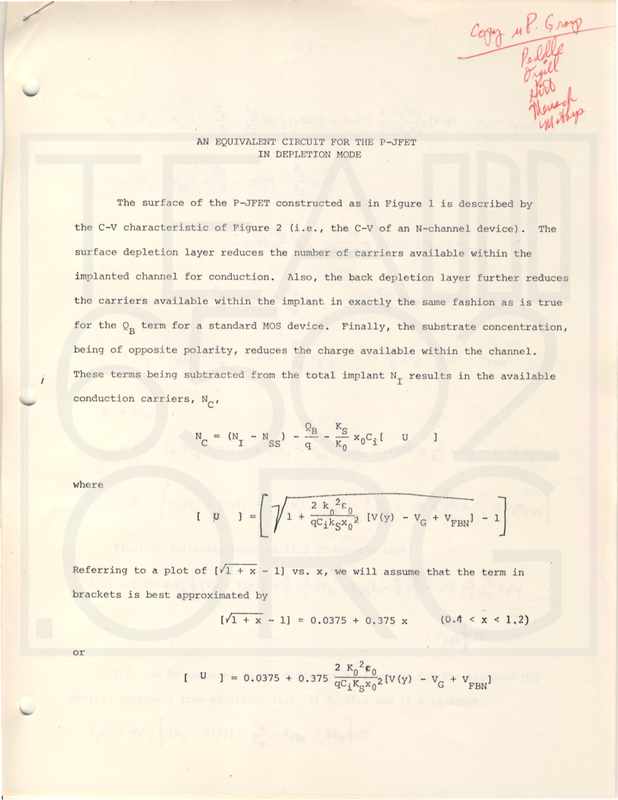

TAB #1: John's Writings

NOTE: "John" refers to MOS Technology Founder and President, John Paivinen.

The next item in the binder is an additional copy of Paivinen's report, Ion Implant Profile Calculations which is archived under Tab #7 of the N-Channel Physical Considerations Binder above.

Tab #2: Depletion Mode Devices

The following articles appear next in binder:

- Implanted Depletion Loads Boost MOS Array Performance by Robert Crawford, Electronics, April 24, 1972

- N-Channel Ion-Implanted Enhancement/Depletion MOSFET'S, by L. Forbes in the IEEE Journal of Solid State Circuits, April 1973

- Implanted Depletion Loads Boost MOS Array Performance by Robert Crawford, Electronics, April 24, 1972

- N-Channel Ion-Implanted Enhancement/Depletion MOSFET'S, by L. Forbes in the IEEE Journal of Solid State Circuits, April 1973

The article Ion Implantation Combined with Silicon-Gate Technology, by C.C. Mai, M. Hswe, and R.B. Palmer, IEEE Transactions on Electron Devices ( Volume: 19 , Issue: 11 , Nov 1972 ) appears next in binder.

The article Doping Profiles by MOSFET Deep Depletion C(V) by D.M. Brown, R.J. Connery, and P.V. Gray, General Electric Company, Research & Development, Schenectady, NY appears next in binder.

Tab #3: Key Articles, Graphs

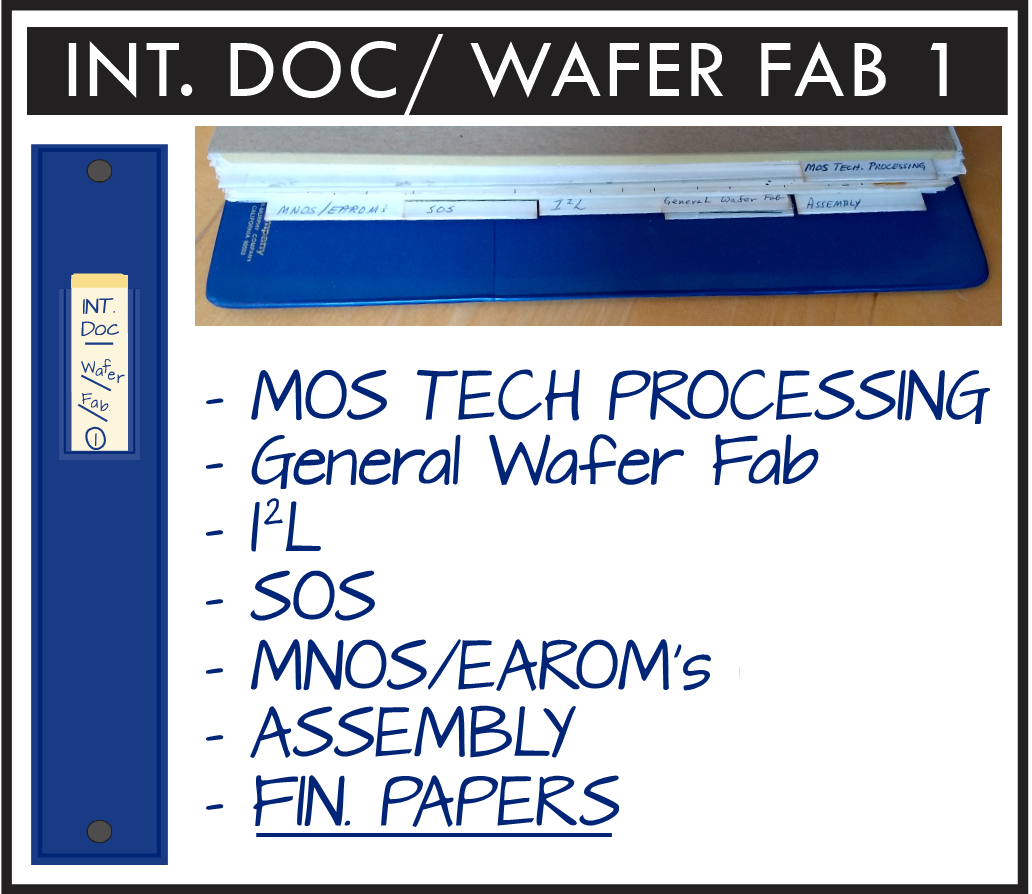

INT. DOC. Wafer Fab 1 Binder

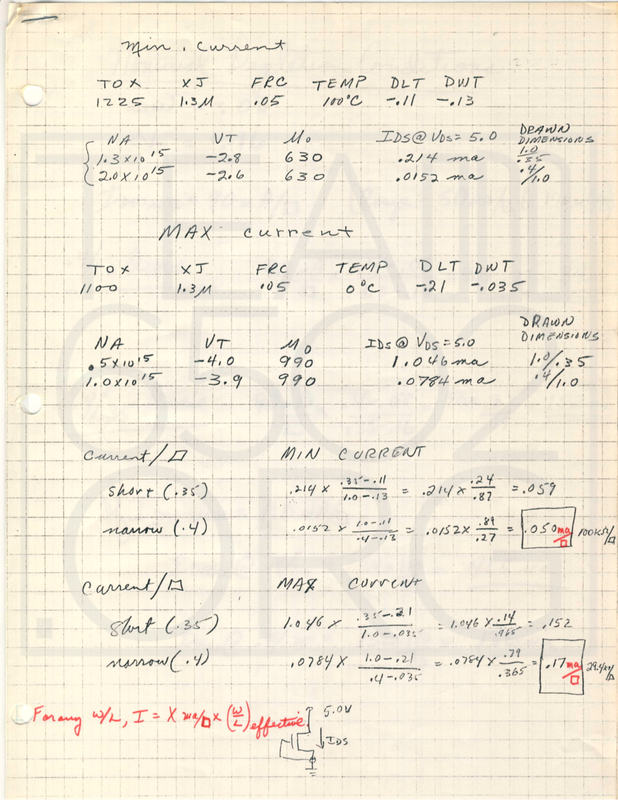

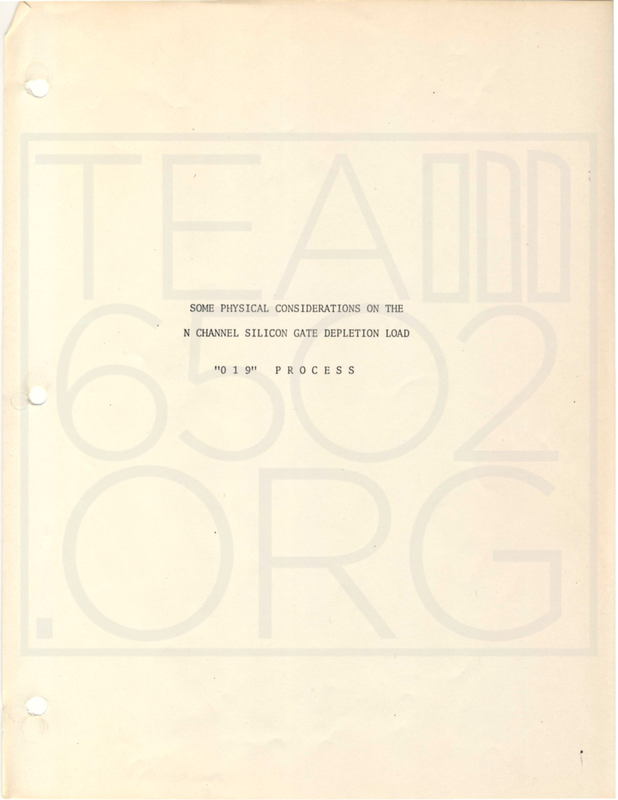

Terry Holdt's INT. DOC Wafer Fab 1 binder contains 7 tabs labeled as noted in the accompanying, above illustration, only a few of which contain documents (the other sections are empty). Of particular interest is the Holdt report, Some Physical Considerations on the N Channel Silicon Gate Depletion Load, found under the the tab MOS Tech Process, which is Holdt's synthesis of information gleaned from meetings, articles, and reports found in the other binders. According to Holdt, his "analysis on the 019 process is not meant to be a rigorous treatment of detailed physics of semiconductor devices, but rather is meant to be of use to the process engineer in analyzing electrical considerations affected by his process decisions and to the design engineer in analyzing process considerations that will affect his electrical parameters." All documents are presented in the order in which they appear in the binder.

Tab #1: MOS Tech Processing

Part 1 of 59 page report, "Some Physical Considerations on the N Channel Silicon Gate Depletion Load '019' Process" written by Terry Holdt. Note that 2 of the items provided as attachments to this document are John Paivinen's reports, "Ion Implant Profile Calculations" which is archived under Tab #7 of the "N-Channel Physical Considerations Binder" and "Effect of Gate Oxide Thickness Variations on Implanted Enhancement and Depletion Devices" which is archived under Tab #1: "John's Writings" of the "Depletion and Ion" binder.

Marketing Materials

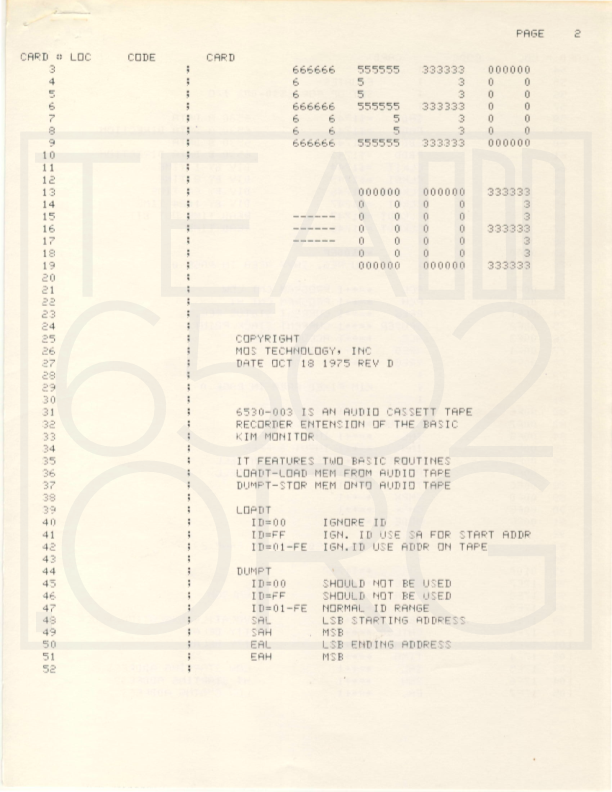

Consumer Instruction Manuals

& Letters to Customers

|

View KIM-1 (and other MOS Technology User Manuals) in their entirety here.

|